# Design of Multiplexers using Reversible Logic Technique

A P Sooriamala<sup>1\*</sup>, V Sherlin Solomi<sup>2</sup>, Reeba Korah<sup>3</sup>, Aby K Thomas<sup>4</sup>

<sup>1\*</sup>Department of Electronics and Communication Engineering,

Hindustan Institute of Technology and Science, Chennai, Tamil Nadu 603103, India.

<sup>\*</sup>Email: sooriavasee@gmail.com

<sup>2</sup>Department of Electronics and Communication Engineering,

Hindustan Institute of Technology and Science, Chennai, Tamil Nadu 603103, India.

Email: vsherlins@hindustanuniv.ac.in

<sup>3</sup>Department of Electronics and Communication Engineering,

Alliance College of Engineering and Design, Alliance University,

Bangalore, Karnataka 562106, India.

Email: reeba.korah@alliance.edu.in

<sup>4</sup>Department of Electronics and Communication Engineering,

Alliance college of Engineering and Design,

Alliance University, Bangalore, Karnataka 562106, India.

Email: aby.thomas@alliance.edu.in

**Abstract**—Reversible logic is promising as it can be applied to different applications in low power like nanocomputing especially in quantum computing. Reversible logic is a technioue for power reduction. Reversible circuits are similar to digital circuits but they work using reversible logic gates. This study focuses on reducing the garbage output and ancilla inputs in reversible multiplexers, thereby reducing the power consumption. In this study two designs of Multiplexers are given. Design1 is using TwinSJ gate and AJ gate. 2:1, 4:1 and 8:1 multiplexers are built. In Design 2, a new gate (SJ gate) is built which functions as 2:1 multiplexer. It has 4\*4 configuration. The inputs are suitably configured so that it performs various logic functions. Using this SJ gate and other basic reversible logic gates, 2:1, 4:1 and 8:1 multiplexers are built. In 2:1 multiplexer, Ancilla inputs are improved to '0' from 5 and garbage output has been reduced to 2 against 7 in existing design. 4:1 multiplexers are built with '0' ancilla inputs against 2 and 11 in existing designs. Garbage output of the proposed 4:1 multiplexer is 5 against 6 and 16 in existing designs. 8:1 multiplexer is built with 1 ancilla input and 11 garbage output against 2 and 12 respectively in existing design. This is designed using VHDL code - xilinx 14.7 for verification purpose and simulated on ISIM.

Keywords: Reversible logic, low power design, multiplexers, garbage output, ancilla input.

## I. INTRODUCTION

Though reversible logic has traceability to year as early as 1973 by C.H. Bennett [1], recently Reversible logic is used in many areas due to its ability to design low loss or approximately loss less digital circuits. According to "Thermodynamics" traditional systems consume energy equal to KTln2 on loss of each it of data as stated by Rolf Landauer [2] in 1961. Here T is the temperature and K is Boltzmann's constant with value equal to 1.380649x10<sup>-23</sup>m<sup>2</sup>kg<sup>2</sup>k<sup>-1</sup>(J/K) [3]. In 1973 C H Bennett correlated the heat loss with information lost. He stated that by reversible logic heat dissipation will be zero [4]. Compared to CMOS, nanotechnology saves more power [5]. This paper focuses on designing multiplexers using the new SJ reversible gate. VHDL coding for reversible gates using which complex circuits are designed. Nanotechnologies, especially Quantumdot Cellular Automata (QCA), gives attractive perspective for future computing technologies [6].

Garbage outputs, gate count, quantum cost, Ancilla input are some of the cost factors in Reversible logic. Different methods for specific cost reductions may be established [7]. In this paper reducing ancilla input and garbage output are focused. Design and implementation of VLSI circuits using Reversible Logic Gates [8] is focused upon to reduce power by reducing the number of garbage outputs and ancilla inputs.

Some of the recent development areas mostly due to pandemic where reversible logic find its application are

- Internet of things (IOT)

- Remote sensing and contactless measurement

- Digital Ink

- online system testing and networking

- wearable computers

# II. REVERSIBLE LOGIC

#### A. Basics of Reversible Logic

Basic Reversible Gates are Feynman, Double Feynman, Toffoli Gate [9], Fredkin Gate, Peres Gate, TSG gate and Sayem Gate. There are gates built for unique applications. Reversible logic devices are used to reduce (theoretically eliminate) power consumption. In reversible logic circuits, number of inputs is equal to the number of outputs [10]. To achieve this ancilla inputs and garage outputs are used. These are not useful for the functioning of the gate. Some combinational circuits[11], D Flipflop, T Flipflop, decoders, latches and RAM cell are built with reduced GO and ancilla Input.

Reversible Logic has the following features

- Same number of outputs as that of inputs.

- Unique input to output pattern.

- Hardware complexity A reduced model.

- Garbage outputs minimized.

- Gate count should be minimum.

- Constant value for inputs ['0' or '1'].

- Fan-out = '0'

- Feedback or Loop back not allowed

Parameters in Reversible Logic Gates

- Quantum cost

- Garbage output

- number of Gates

Reversible logic is very essential for the construction of low power, low loss computational structures which are very essential for construction of arithmetic circuits used in quantum computation and other low power digital circuits [12].

## B. Reversible Logic gates

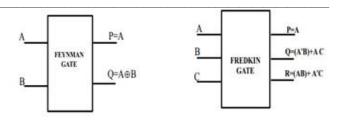

There are different cost considerations in Reversible logic. Garbage outputs, gate count, quantum cost, Ancilla input are to name few [13]. Different methods for specific cost reductions may be established. In this paper reducing ancilla input and garbage output are focused. In modern digital world, low power design in both analog and digital VLSI circuits attracts more attention [14]. Design and implementation of VLSI circuits using Reversible Logic Gates [14] is focused upon to reduce power by reducing the number of garbage outputs and ancilla inputs [15]. Basic Gates used in this study are Feynman gate and FREDKIN Gate. Their block diagram are given in Fig.1. Feynman gate is used to avoid fan out. Fredkin gate is used for other functions. AJ gate has the functionality of AND and OR gate.

Figure 1. FEYNMAN Gate & FREDKIN Gate

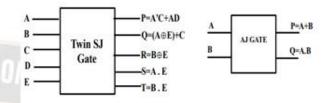

Figure 2. TWIN SJ Gate & AJ Gate

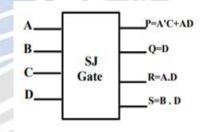

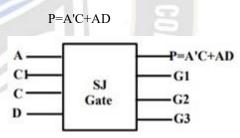

To build the circuit under study, SJ gate is designed and some basic reversible gates are used. By configuring the inputs properly, SJ gate can be used to perform some logical functions. SJ gate is used as a 2:1 multiplexer. Based on the state of A (0 or 1), either B or C is selected at output 'P'.

Figure 3. SJ Gate TABLE I. TRUTH TABLE – SJ GATE

|   | IN | NPUT |   | OUTPUT       |     |       |           |  |

|---|----|------|---|--------------|-----|-------|-----------|--|

| А | В  | С    | D | P=A'C<br>+AD | Q=D | R=A.D | S=B.<br>D |  |

| 0 | 0  | 0    | 0 | 0            | 0   | 0     | 0         |  |

| 0 | 0  | 0    | 1 | 0            | 1   | 0     | 0         |  |

| 0 | 0  | 1    | 0 | 1            | 0   | 0     | 0         |  |

| 0 | 0  | 1    | 1 | 1            | 1   | 0     | 0         |  |

| 0 | 1  | 0    | 0 | 0            | 0   | 0     | 0         |  |

| 0 | 1  | 0    | 1 | 0            | 1   | 0     | 1         |  |

| 0 | 1  | 1    | 0 | 1            | 0   | 0     | 0         |  |

| 0 | 1  | 1    | 1 | 1            | 1   | 0     | 1         |  |

| 1 | 0  | 0    | 0 | 0            | 0   | 0     | 0         |  |

| 1 | 0  | 0    | 1 | 1            | 1   | 1     | 0         |  |

| 1 | 0  | 1    | 0 | 0            | 0   | 0     | 0         |  |

| 1 | 0  | 1    | 1 | 1            | 1   | 1     | 0         |  |

| _ | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|---|

|   | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

|   | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

|   | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

|   |   |   |   | - | - | - | - |   |

|   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

|   |   |   |   |   |   |   |   |   |

# III. REVERSIBLE LOGIC IMPLEMENTATION

#### A. Related Study

Reversible Multiplexers using gates like Feynman, Fredkin, BJN and Peres gates. This design has more number of GO, CI and number of gates. In this work 4:1 multiplexer is built using different basic RL gates and BJN gate. It has 4 constant inputs and 10 garbage outputs. Using Feynman gate, Peres Gate and Fredkin Gates and a new BJN gate. This complicates the Fabrication, as different gates need to be integrated. A new reversible gate COG is built, which is used as 2:1 multiplexer. COG is a 3\*3 Controlled Operation Gate. In this the authors have compared the conventional multiplexers with reversible multiplexers for Cost metrics and number of gates. Rather than Number of gates, quantum cost can be used as a metrics. Comparison of number of gates does not give clear picture about the chip area, as different gates occupy different area based on the number of Transistors used. Any reversible gate has many basic logic gates [16].

Fredkin gate is used as 2:1 multiplexer and focus is on fabrication. Previously researchers observed the system built 2:1 multiplexer, D Flip Flop and PIPO shift register using reversible gates. They have constructed the 2:1 multiplexer with 3 constant inputs and 8 garbage outputs. It is built using Proposed study has a 2:1 Feynman and Toffoli gates. multiplexer with 1 constant input and 3 garbage outputs. In the paper [18] 8:1 multiplexer is built using 4:1 multiplexer in which Fredkin gate is used as 2:1 multiplexer. In this design, though the authors claim 7 garbage output and 0 constant input actually 12 garbage outputs and 2 constant inputs are there. In the proposed design 8:1 multiplexer is built with reduced number of garbage outputs. 4:1 multiplexer is built in 2 approaches. One approach uses 3 TKS gates and other approach is with a VSMT gate. No of reversible gates used and Garbage outputs are compared for both approaches and confirmed that the second approach is better than the first one. Where a 8:1 multiplexer is built using 1 TKS gate and 2 VSMT gates. No of gates and Garbage outputs are the parameters verified [19].

A 4:1 multiplexer is built with 43 quantum cost, 11constant inputs and 16 garbage outputs. There is scope for reduction of garbage output and constant input [20]. In the proposed work it has been reduced to 0 constant input and 5 garbage output.

In this paper different Boolean functions are built using Feynman, Fredkin and Sayem gates. 4:1 multiplexer and D Flip

Flop are built. Power, delay, GO and CI of the 4:1 multiplexer are compared with the existing design. The design has 6GO and 2 CI. This is reduced in the proposed design

## B. Proposed Study

*Reversible Multiplexer:* Multiplexer is a data selector. Out of multiple inputs one is connected to the output. This selection is done by selection bits (S0, S1...). Out of  $2^N$  input signals one input is selected using N select signals.

This work focuses on building multiplexers with less garbage output and less ancilla input. The authors propose two designs.

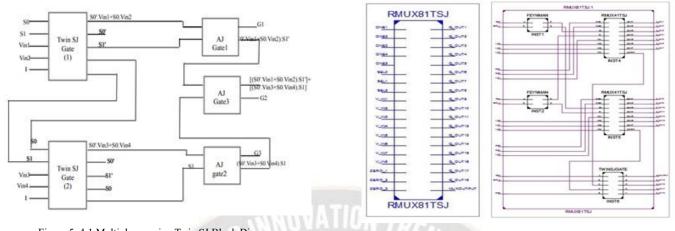

*Design 1:* In Design1 multiplexers are built using TWINSJ a 5x5 gate and AJ gate.

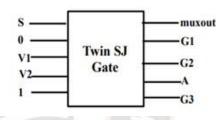

*Multiplexer 2:1:* TwinSJ gate acts as 2:1 multiplexer. Fig 4 shows the TwinSJ gate configured as 2:1 multiplexer. Output 'P'of the TwinSJ gate is the muxoutput of the 2:1 multiplexer. A is the selection bit and C and D are the inputs. B and E are the ancilla inputs and G1, G2 and G3 are the garbage outputs. Simulation results of 2:1 multiplexer are shown in \*\*.

Figure 4. 2:1 Multiplexer using Twin SJ Gate

*Multiplexer* 4:1: The component under study is a 4:1 multiplexer. Multiplexer is a data selector. Out of various inputs one is selected to the output. This selection is done by selection bits. Out of  $2^N$  input signals one input is selected using N select signals. Inputs may be Analog or digital signal. In this paper, 8:1 multiplexer is built using 4:1 multiplexers. 4:1 multiplexer circuit is built using three numbers of 2:1 multiplexer. 2:1 multiplexer is built using two FEYNMAN gates which is a reversible gate. FEYNMAN gate is a copier gate. If one of the inputs (B) is made 0, the other input (A) is available at both outputs. Output of a 4:1 multiplexer is

## [(S0'.Vin1+S0.Vin2).S1'] + [(S0'.Vin3+S0.Vin4).S1]

Where Vin1, Vin2, Vin3 and Vin4 are input signals. Out of these, one signal needs to be connected or selected at the output. Two select signals S0 and S1 are available. In combination of 00, 01, 10 and 11, select signals can be configured to select Vin1, Vin2, Vin3 and Vin4 respectively.

Figure 5. 4:1 Multiplexer using Twin SJ Block Diagram

Two TWINSJ gates and three AJ gates are used in 4:1 multiplexer. TWINSJ gate has the functionality of a 2:1 multiplexer and Feynman gates (repeater). In TWINSJ gate 1, When E input is High ('1'), s0 and s1 are available at S and T outputs. Vin1 and Vin2 are the inputs to TWINSJ gate1. Vin3 and Vin4 are input to Gate 2. AJ gate has the functionality of AND and OR gates. Output of AJ gate 3 is the selected output.

Muxout=[(S0'.Vin1+S0.Vin2).S1']+[(S0'.Vin3+S0.Vin4).S

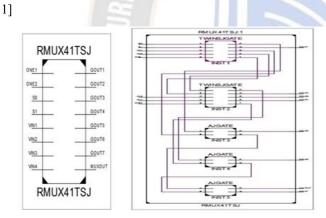

Figure 6. 4:1 Multiplexer using Twin SJ

*Multiplexer 8:1:* selects one out of 8 inputs. In this paper, 8:1 multiplexer is built using two 4:1 multiplexers and a TWINSJ gate. FEYNMAN gate is a copier gate used to repeat the signals as Fanout is not possible. If B is made as '0', then A is available at both output points.

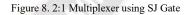

*Design 2:* uses SJ gate and Fredkin gates to build multiplexer circuits. In the proposed design2 number of garbage outputs and ancilla inputs are reduced.

Multiplexer 2:1: SJ gate acts as 2:1 multiplexer. Fig 7 shows the SJ gate configured as 2:1 multiplexer. Output 'P'of the SJ gate is the muxoutput of the 2:1 multiplexer. 'P' is the muxoutput. P=A'C+AD where A is the selection bit and C and D are the inputs. C1 is the ancilla input and G1, G2 and G3 are the garbage outputs. Simulation results of 2:1 multiplexer are shown in Fig.6.

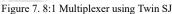

*Multiplexer 4:1:* 4:1 Multiplexer is built using three SJ gates. Output of 4:1 multiplexer is

#### "Muxout=[(S0'.Vin1+S0.Vin2).S1']+[(S0'.Vin3+S0.Vin4).S]"

Where Vin1, Vin2, Vin3 and Vin4 are input signals. Out of these, one signal is connected or selected at the output. Two select signals S0 and S1 are available. In combination of 00, 01, 10 and 11, select signals can be configured to select Vin1, Vin2, Vin3 and Vin4 respectively. Three SJ gates are used to build a 4:1 multiplexer. SJ gate does the functionality of a 2:1 multiplexer. In SJ gate1, S1 is available at Q output as a repeater. Vin1 and Vin2 are the inputs to SJ gate1. Vin3 and Vin4 are inputs to SJ gate2.

Muxout=[(S0'.VIN1+S0.VIN2).S1']+[(S0'.VIN3+S0.VIN4).S1] is from the third gate.

Figure 9. 4:1 multiplexer using SJ gate

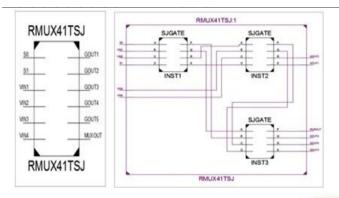

*Multiplexer 8:1:* 8:1 multiplexer is built using SJ gates and FREDKIN gates. Eight inputs V\_IN1 to V\_IN8 are fed to SJ gates and Fredkin gates. Suitably using Feynman gates the select signals are reused. SEL0 and SEL1 are used in the circuit using copier gate (FEYNMAN gate).

Outputs of SJ gates are selected as "muxoutput" using a FREDKIN gate with SEL3 as the selection bit. Five SJ gates, one Feynman gate and two Fredkin gates are used. SJ gate acts as copying gate also. Some of the outputs are reused to reduce the ancilla inputs and garbage outputs.

Muxout=[(S0'.VIN1+S0.VIN2).S1'S2']+[(S0'.VIN3+S0.VI N4).S1S2']+[(S0'.VIN5+S0.VIN6).S1'S2]+[(S0'.VIN7+S0.VI N8).S1S2]

Various combination of selection signals are given and corresponding multiplexer output is noted. This has been verified and results are shown in the Fig.7. One ancilla input and 11 garbage outputs are used.

Figure 10. 8:1 multiplexer using SJ gate

# IV. SIMULATION & RESULT

All circuits are coded on Xilinx tool using VHDL coding, simulated and verified for reduced garbage output and ancilla input. A. Multiplexer 2:1

P output of SJ gate is the muxoutput of the 2:1 multiplexer. If A =0, B is selected at the output and if A = 1, then C is there at the output. Fig 6 shows the result.

| File Edit View | Simulation | Window Layout Help                                                                      |

|----------------|------------|-----------------------------------------------------------------------------------------|

| ) ờ 🖥 😓 🐰      | 6 X 8      | 10 여 🖄 🐹 🕴 🖗 🗄 🗉 😳 🌶 😢 🏓 🎉 🏓 这 🍲 🛊 수 속 🖬 🕨 🗐 🕼 🖬 😡 Relax                                |

|                |            | 1.6                                                                                     |

| Name           | Value      | 10.0 us . 10.2 us . 10.4 us . 10.6 us . 10.8 us . 11.0 us . 11.2 us . 11.4 us . 11.5 us |

| The st         | value      |                                                                                         |

| 148 v2         | 0          |                                                                                         |

| là s           | 1          |                                                                                         |

| 🖓 muxout       | 0          |                                                                                         |

|                |            |                                                                                         |

Figure 11. 2:1 Multiplexer Simulation Result

# B. Multiplexer 4:1

In the sample, to show the results clearly, Vin1 is chosen as 100ns ON and 100ns OFF signal, Vin2 is 100ns ON and 20ns OFF, Vin3 is 20ns ON and100ns OFF and Vin4 is 40ns ON and 200ns OFF. In the fig.7 status of S0 and S1 at different timing and corresponding muxout can be checked. When S0='1' and S1='0', Vin2 is at the output, S0='0' and S1='1', Vin3 is at the output. When S0='1' and S1='1', Vin4 is there at the output.

Figure 12. 4:1 Multiplexer Simulation Result

#### C. Multiplexer 8:1

Based on the 3 selection bits, one of the eight inputs is selected at the output. To show the difference in the output, signals with different timings are used. When SEL0, SEL1 and SEL2 are all 0, V\_IN1 is available at the output. When SEL0 is made to '1' at 0.12  $\mu$ sec, V\_IN2 is selected at output. When SEL0 is made to '0' and SEL1 is made to '1' at 2.5  $\mu$ sec, V\_IN3 is selected at output. At 3.5  $\mu$ sec, SEL0 and SEL1 are made to '1', V\_IN4 is selected at output. Similarly for all combinations of selection bits, 100, 101, 110, and 111 the output is verified. At 7.5  $\mu$ sec SEL0, SEL1 and SEL2 are '1' and V\_IN8 is available at the output. Simulation results are shown in Fig.8.

Figure 13. 8:1 Multiplexer Simulation Result

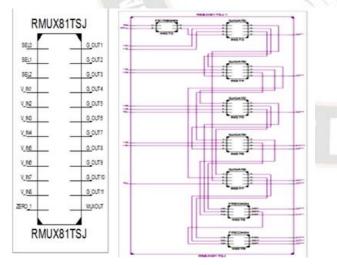

The table 2 shows the comparison Design1 and Design2. Table 3 shows comparison of various reversible multiplexers designed with the existing design. These designs are compared for Garbage output and ancilla input. Every proposed design is compared with the existing designs and improvement achieved are given. Fig.14 shows the results.

| Multiplexer<br>circuit | De               | esign 1           | Design 2         |                   |  |

|------------------------|------------------|-------------------|------------------|-------------------|--|

|                        | Ancilla<br>input | Garbage<br>output | Ancilla<br>input | Garbage<br>output |  |

| 2:1 multiplexer        | 2                | 4                 | 1                | 3                 |  |

| 4:1 multiplexer        | 2                | 7                 | 0                | 5                 |  |

|                        |                  |                   |                  |                   |  |

| TABLE II COMPARISON OF DES | SIGN1 & DESIGN 2 |

|----------------------------|------------------|

|----------------------------|------------------|

|                            | Existir              | ng design             | Proposed         | l Design              | Improvement %    |                           |

|----------------------------|----------------------|-----------------------|------------------|-----------------------|------------------|---------------------------|

| Multiplexer<br>circuit     | Ancill<br>a<br>Input | Garbag<br>e<br>Output | Ancilla<br>Input | Garbag<br>e<br>Output | Ancilla<br>Input | Garba<br>ge<br>Outpu<br>t |

| 2:1<br>Multiplexer[8]      | 5                    | 7                     | 0                | 2                     | 100.00%          | 71.43<br>%                |

| 4:1<br>Multiplexer[14<br>] | 2                    | 6                     | 0                | 5                     | 100.00%          | 16.67<br>%                |

| 8:1<br>Multiplexer[7]      | 2                    | 12                    | 1                | 11                    | 50.00%           | 8.33%                     |

TABLE III. COMPARISON OF ANCILLA INPUT AND GARBAGE OUTPUT

8:1 multiplexer

# V. CONCLUSION

Reversible multiplexers of 2:1, 4:1 and 8:1 configuration are designed using Reversible Twin SJ gate (Design1) and SJ gate (Design2). Comparison with existing designs for garbage outputs and ancilla inputs shows the proposed design2 of reversible multiplexers are improved over the existing design in terms of garbage outputs and ancilla inputs. In the proposed design of 2:1, and 4:1 multiplexers using SJ gate there is '0' Ancilla input. 8:1 multiplexer is designed with 1 ancilla input. Similarly 2:1 multiplexer is designed with 2 garbage outputs (71.43% improvement), 4:1 multiplexer is designed with 5 Garbage outputs (16.67% improvement) and 8:1 multiplexer is designed with 11 garbage output (8.33% improvement). As multiplexer is an important element in CPU for selection of peripheral devices and memory accessing, this improvement will be helpful in design of low power computers and future system design

#### ACKNOWLEDGMENT

None.

## REFERENCES

- C.H. Bennett, "Logical Reversibility of computation," IBM Journal of Research and Development, pp 525-532, 1973.

- [2] R. Landauer, "Irreversibility and heat generation in the computing process," IBM Journal of Research and Development, vol. 5, pp. 183-191, 1961.

- [3] D. Goyal, and V. Sharma, VHDL Implementation of Reversible Logic Gates Journal of Advanced Technology & Engineering Research (IJATER) vol. 2, no. 3, May. 2012.

- [4] S. Gugnani, and A. Kumar, "Synthesis of Reversible Multiplexers," International Journal of Scientific & Engineering Research, vol. 4, no. 7, p. 1859, Jul. 2013.

- [5] V. Shukla, O. P. Singh, G. R. Mishra, and R. K. Tiwari, "An Optimized Circuit of 8:1 Multiplexer Circuit using Reversible Logic Gates," International Journal of Computer Applications (0975 – 8887) International Conference on Communication,

Computing and Information Technology (ICCCMIT-2014).

- [6] S. Mamataj, B. Das, A. Rahaman, "Realization of Different Multiplexers by Using COG Reversible Gate," International Journal of Electronics and Electrical Engineering, vol. 3, no. 5, Oct. 2015

- [7] N.Pannu, and N. R.Prakash, "A Power-Efcient Multiplexer using Reversible Logic," Microelectronics Journal (ELSEVIER), vol. 53, pp. 25–34, 2016. Indian Journal of Science and Technology, vol. 9, no. 30, Aug. 2016.

- [8] J. N. Ravi, A. M. Vijay Prakash, S. Madan, "Design and Implementation of Digital Components Using Reversible Logic Gates," International Journal of Technical Research & Science (IJTRS), p. 70, Mar. 2017.

- [9] S. Mann, and R. Jain, "Design and Analysis of Reversible Multiplexer and Demultiplexer using R-Gates," Proceeding International conference on Recent Innovations is Signal Processing and Embedded Systems (RISE -2017), pp. 27-29 Oct. 2017

- [10] G. Sreekanth, C. Venkata Sudhakar, "Design and Synthesis of Combinational Circuits using Reversible Logic," International Journal of Electronics, Electrical and Computational System IJEECS, vol. 7, no. 4 Apr. 2018.

- [11] A. M. Chabi, A. Roohi, H. Khademolhosseini, S. Sheikhfaal, S. Angizi, K. Navi, and R. F. DeMara, Towards ultra-efficient QCA reversible circuits," Microprocessors and Microsystems, vol. 49, Mar. 2017, pp. 127-138

- [12] H. M. Gaur, A.K. Singh, and U. Ghanekar, "In-depth Comparative Analysis of Reversible Gates for DesigningLogic Circuits," Procedia Computer Science, vol. 125, pp. 810-817, 2018, 6th International Conference on Smart Computing & Communications.

- [13] D. Krishnavenia, M. Geetha Priya, "Design of a new BUS for low power reversible computation," Computers and Electrical Engineering, vol. 89, p. 106938, 2021.

- [14] A.K. Rajput, S. Chouhan, M. Pattanaik, "Low Power Boolean

**URITES**

Logic Circuits using Reversible Logic Gates Auckland University of Technology," 2019 International Conference on Advances in Computing, Communication and Control (ICAC3)-IEEE Xplore, Mar. 2020.

- [15] A. P. Sooriamala, A.K. Thomas, R. Korah, "Study On Reversible Logic Circuits And Analysis," Alliance International Conference on Artificial Intelligence and Machine Learning (AICAAM), Apr. 2019.

- [16] A.P. Sooriamala, A.K. Thomas, R. Korah, "Reduction of Garbage Outputs and Constant Inputs in Design of Combinational Circuits Using Reversible Logic," 2021 Sixth International Conference on WirelessCommunications, Signal Proc.essing and Networking (WiSPNET), 2021.

- [17] A. P. Sooriamala, A.K. Thomas, R. Korah, "Design And Study Of Circuits Using Reversible Logic," IEEE 2nd International Conference on Electronics and Sustainable Communication Systems ICESC, pp. 4-6, Aug. 2021.

- [18] Wiling, B. (2021). Locust Genetic Image Processing Classification Model-Based Brain Tumor Classification in MRI Images for Early Diagnosis. Machine Learning Applications in Engineering Education and Management, 1(1), 19 - 23. Retrieved from http://yashikajournals.com/index.php/mlaeem/article/view/6

- [19] K.C. Koteswaramma, A. Shreya, N.H. Vardhan, K. Tarun, S.C. Venkateswarlu, and V. Vijay, "ASIC Implementation of division circuit using reversible logic gates applicable in ALUs," In Innovations in Signal Processing and Embedded Systems, Springer, Singapore pp. 119-132, 2023.

- [20] G. V. Vinod, D.V. Kumar and N. M. Ramalingeswararao, "An Innovative Design of Decoder Circuit using Reversible Logic," Journal of VLSI circuits and systems, vol. 4, no. 01, pp.1-6, 2022.

- [21] S. S. Samrin, R. Patil, S. Itagi, S.C. Chetti, and A. Tasneem, Design of Logic Gates using Reversible Gates with Reduced Quantum Cost. Global Transitions Proceedings. 2022.